### TM7100 Series Notebook Computer

### **Service Guide**

PART NO.: 49.42A01.001 DOC. NO.: SG238-9712A

PRINTED IN TAIWAN

### Copyright

Copyright © 1997 by Acer Incorporated. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written permission of Acer Incorporated.

#### Disclaimer

Acer Incorporated makes no representations or warranties, either expressed or implied, with respect to the contents hereof and specifically disclaims any warranties of merchantability or fitness for any particular purpose. Any Acer Incorporated software described in this manual is sold or licensed "as is". Should the programs prove defective following their purchase, the buyer (and not Acer Incorporated, its distributor, or its dealer) assumes the entire cost of all necessary servicing, repair, and any incidental or consequential damages resulting from any defect in the software. Further, Acer Incorporated reserves the right to revise this publication and to make changes from time to time in the contents hereof without obligation of Acer Incorporated to notify any person of such revision or changes.

Intel is a registered trademark and Pentium is a trademark of Intel Corporation. Other brand and product names are trademarks and/or registered trademarks of their respective holders.

### About this Manual

### Purpose

This service guide aims to furnish technical information to the service engineers and advanced users when upgrading, configuring, or repairing the TM7100 series notebook computer.

### **Manual Structure**

This service guide contains technical information about the TM7100 series notebook computer. It consists of three chapters and five appendices.

#### Chapter 1 System Introduction

This chapter describes the system features and major components. It contains the TM7100 series notebook computer board layout, block diagrams, cache and memory configurations, power management and mechanical specifications.

#### Chapter 2 Major Chips Description

This chapter describes the features and functions of the major chipsets used in the system board. It also includes chipset block diagrams, pin diagrams, and pin descriptions.

#### Chapter 3 BIOS Setup Utility

This chapter describes the parameters in the BIOS Utility screens.

#### Chapter 4 Disassembly and Unit Replacement

This chapter describes how to disassemble the TM7100 series notebook computer to make replacements or upgrades.

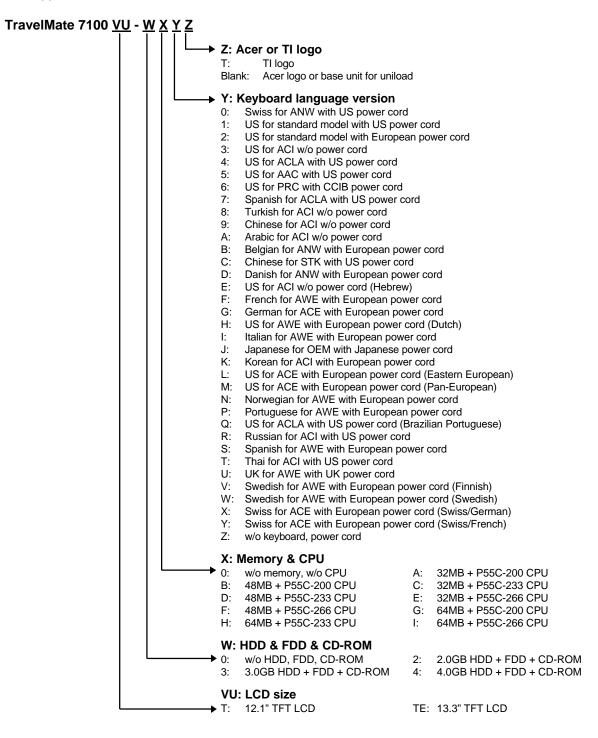

#### Appendix A Model Number Definition

This appendix shows the different configuration options for the TM7100 series notebook computer.

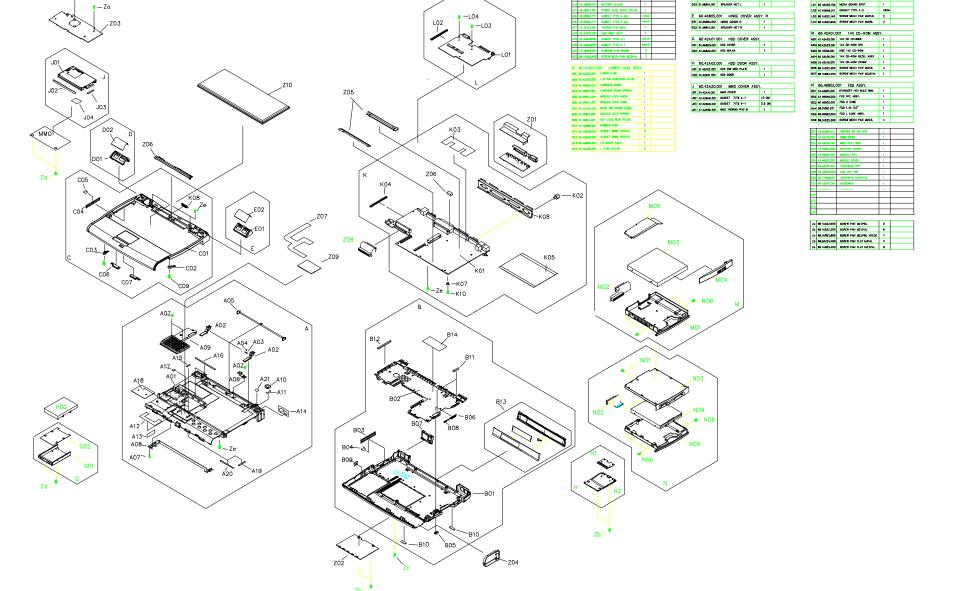

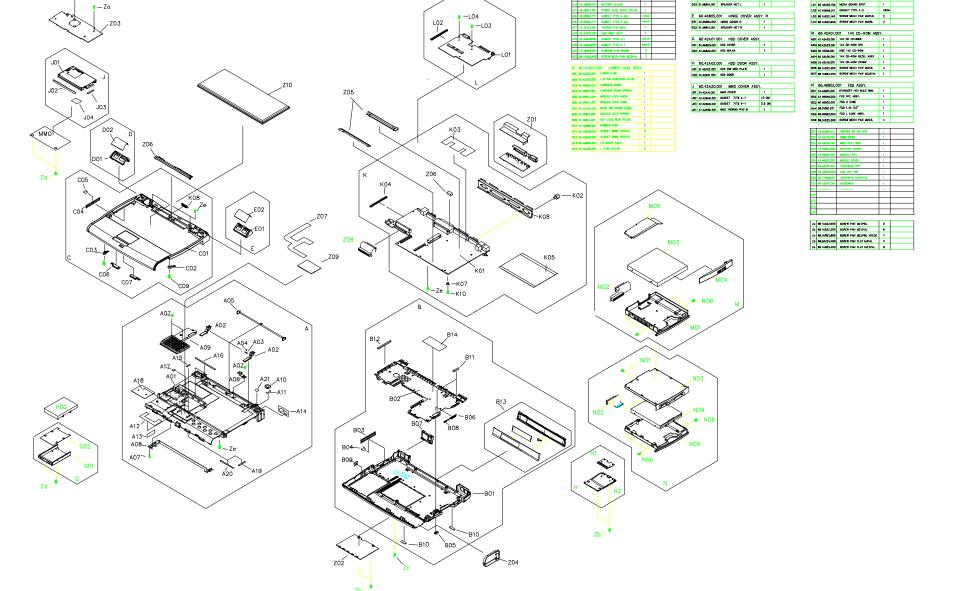

#### Appendix B Exploded View Diagram

This appendix illustrates the system board and CPU silk screens.

#### Appendix C Spare Parts List

This appendix lists the spare parts for the TM7100 series notebook computer with their part numbers and other information.

#### Appendix D **Schematics**

This appendix contains the schematic diagrams for the system board.

#### Appendix E **BIOS POST Checkpoints**

This appendix lists and describes the BIOS POST checkpoints.

### Conventions

The following are the conventions used in this manual:

Text entered by user

#### WARNING

doing specific actions.

#### **IMPORTANT**

Reminds you to do specific actions relevant to the accomplishment of procedures.

#### TIP

Tells how to accomplish a procedure with minimum steps through little shortcuts.

Denotes actual messages that appear onscreen.

Represent the actual keys that you have to press on the keyboard.

### NOTE

Gives bits and pieces of additional information related to the current topic.

Alerts you to any damage that might result from doing or not

### CAUTION

Gives precautionary measures to avoid possible hardware or software problems.

### **Table of Contents**

### Chapter 1 System Introduction

| 1.1 Features |         | 1-1                               |      |

|--------------|---------|-----------------------------------|------|

|              | 1.1.2   | FlashStart Automatic Power-On     | 1-2  |

| 1.2          | Ports   |                                   | 1-3  |

|              | 1.2.1   | Rear Panel Ports                  | 1-3  |

|              | 1.2.2   | Left Panel Ports                  | 1-4  |

|              | 1.2.3   | Indicator Lights                  | 1-5  |

|              | 1.2.4   | Hot Keys                          | 1-6  |

|              | 1.2.5   | Automatic Tilt                    | 1-8  |

| 1.3          | System  | Specification Overview            | 1-9  |

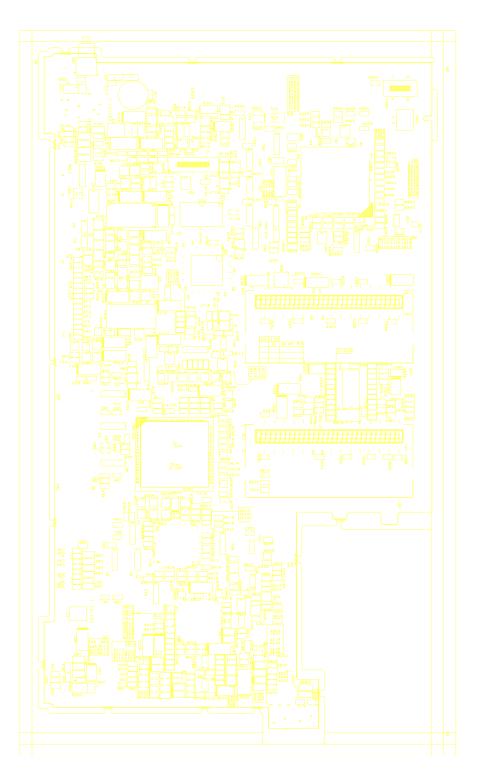

| 1.4          | Board L | ayout                             | 1-11 |

|              | 1.4.1   | System Board (Top Side)           | 1-12 |

|              | 1.4.2   | System Board (Bottom Side)        | 1-13 |

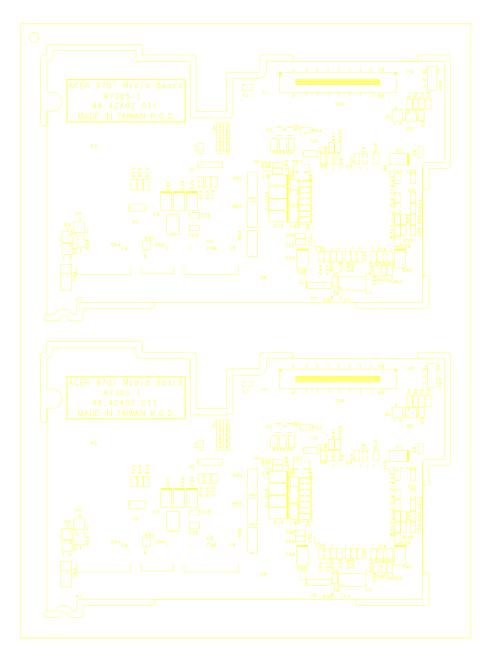

|              | 1.4.3   | Media Board (Top Side)            | 1-14 |

|              | 1.4.4   | Media Board (Bottom Side)         | 1-15 |

| 1.5          | Jumper  | s and Connectors                  | 1-16 |

|              | 1.5.1   | Mainboard                         | 1-16 |

|              | 1.5.2   | Media Board                       | 1-18 |

| 1.6          | System  | Configurations and Specifications | 1-19 |

|              | 1.6.1   | System Memory Map                 | 1-19 |

|              | 1.6.2   | Interrupt Channel Map             | 1-19 |

|              | 1.6.3   | I/O Address Map                   | 1-19 |

|              | 1.6.4   | DMA Channel Map                   | 1-20 |

|              | 1.6.5   | GPIO Port Definition Map          | 1-21 |

|              | 1.6.6   | PCI Devices Assignment            | 1-25 |

|              | 1.6.7   | Power Management                  | 1-25 |

|              | 1.6.8   | CPU Module                        | 1-31 |

|              | 1.6.9   | BIOS                              | 1-32 |

|              | 1.6.10  | System Memory                     | 1-32 |

|              | 1.6.11  | Video Memory                      | 1-33 |

|              | 1.6.12  | Video Display Modes               | 1-34 |

|              | 1.6.13  | Audio                             | 1-35 |

|     | 1.6.14                        | 6.14 PCMCIA1-3                     |   |

|-----|-------------------------------|------------------------------------|---|

|     | 1.6.15                        | Parallel Port1-3                   | 6 |

|     | 1.6.16                        | Serial Port1-3                     | 6 |

|     | 1.6.17                        | Touchpad1-3                        | 6 |

|     | 1.6.18                        | SIR/FIR1-3                         | 7 |

|     | 1.6.19                        | LCD1-3                             | 7 |

|     | 1.6.20                        | CD-ROM1-3                          | 8 |

|     | 1.6.21                        | Diskette Drive1-3                  | 8 |

|     | 1.6.22                        | Hard Disk Drive1-3                 | 9 |

|     | 1.6.23                        | Keyboard1-3                        | 9 |

|     | 1.6.24                        | Battery1-4                         | 0 |

|     | 1.6.25                        | DC-DC Converter1-4                 | 0 |

|     | 1.6.26                        | DC-AC Inverter1-4                  | 1 |

|     | 1.6.27                        | AC Adapter1-4                      | 1 |

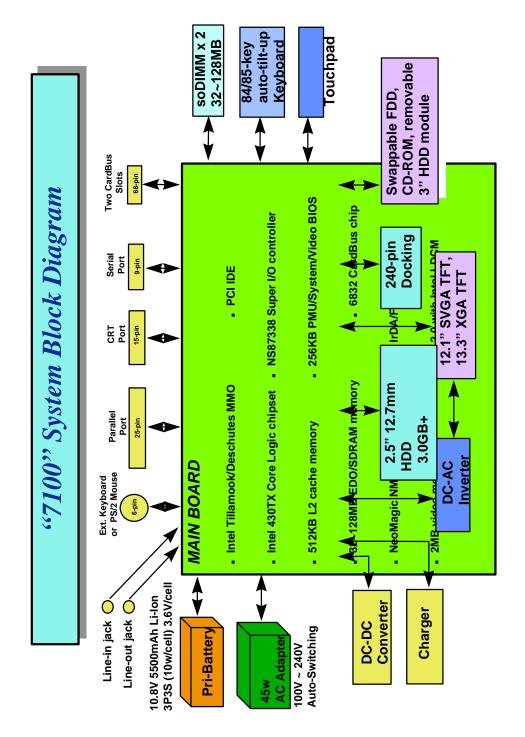

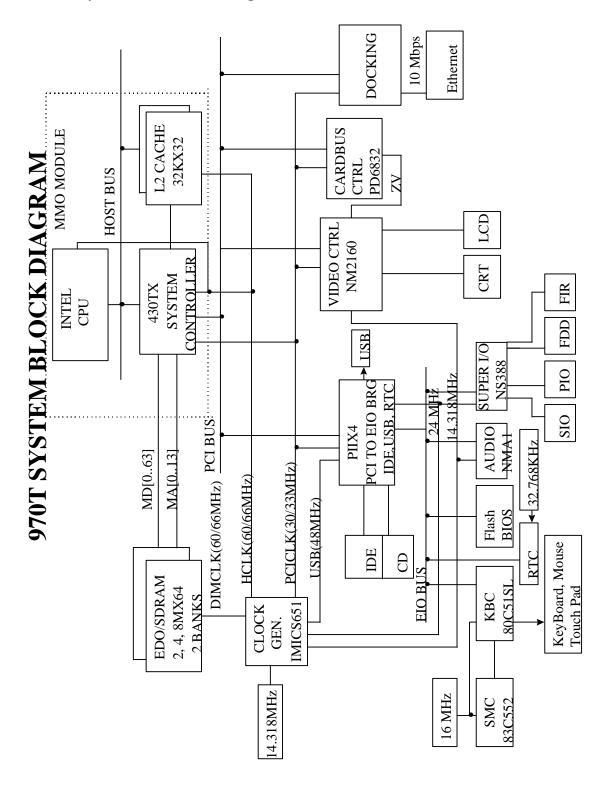

| 1.7 | System I                      | Block Diagrams1-4                  | 2 |

|     | 1.7.1                         | System Functional Block Diagram1-4 | 2 |

|     | 1.7.2                         | System Bus Block Diagram1-4        | 3 |

| 1.8 | Environn                      | nental Requirements1-4             | 4 |

| 1.9 | Mechanical Specifications1-45 |                                    |   |

### Chapter 2 Major Chips Description

| 2.1 | Major C   | Major Component List2-     |      |

|-----|-----------|----------------------------|------|

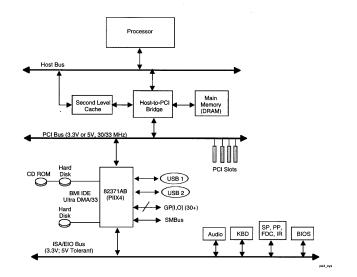

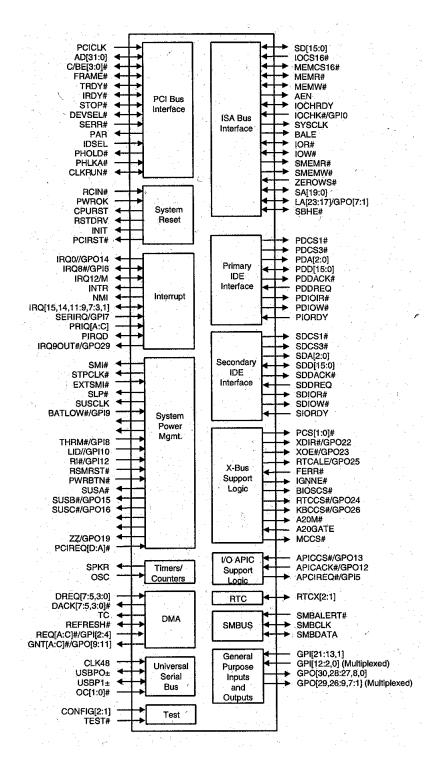

| 2.2 | Intel PII | X4                         | 2-2  |

|     | 2.2.1     | Features                   | 2-4  |

|     | 2.2.2     | Architecture Block Diagram | 2-6  |

|     | 2.2.3     | Block Diagram              | 2-7  |

|     | 2.2.4     | Pin Descriptions           | 2-8  |

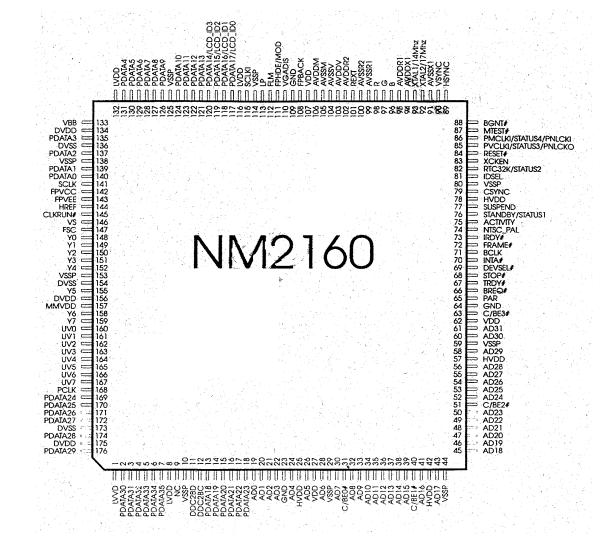

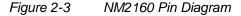

| 2.3 | NM2160    | )                          | 2-28 |

|     | 2.3.1     | Features                   | 2-28 |

|     | 2.3.2     | Pin Diagram                | 2-30 |

|     | 2.3.3     | Pin Descriptions           | 2-31 |

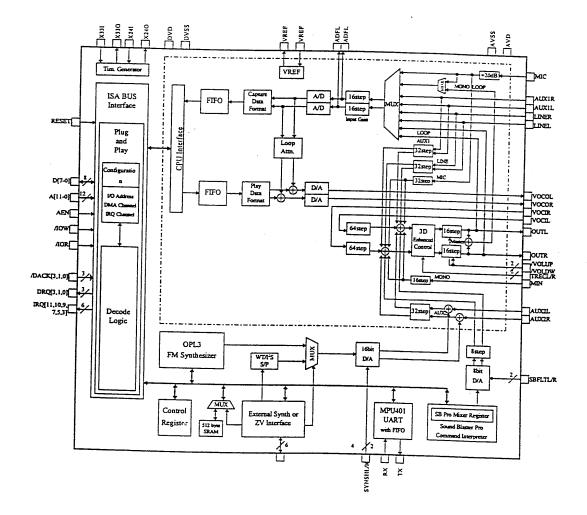

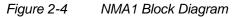

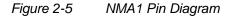

| 2.4 | NMA1      |                            | 2-38 |

|     | 2.4.1     | Features                   | 2-38 |

|     | 2.4.2     | Block Diagram              | 2-39 |

|         | 2.4.3     | Pin Diagram                         | 2-40 |

|---------|-----------|-------------------------------------|------|

|         | 2.4.4     | Pin Descriptions                    | 2-41 |

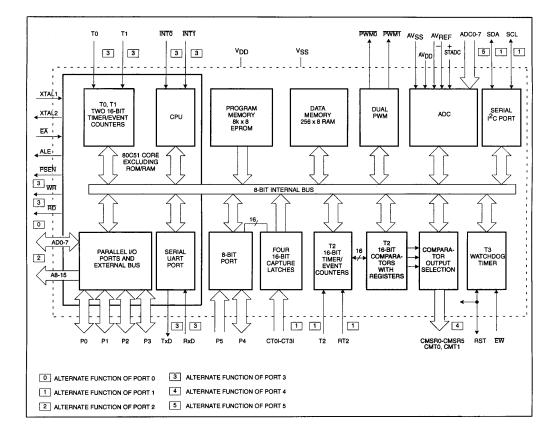

| 2.5     | Philips 8 | 37C552 System Management Controller | 2-43 |

|         | 2.5.1     | Features                            | 2-43 |

|         | 2.5.2     | Block Diagram                       | 2-44 |

|         | 2.5.3     | Pin Diagram                         | 2-45 |

|         | 2.5.4     | Pin Descriptions                    | 2-46 |

| 2.6     | NS8733    | 88VJG Super I/O Controller          | 2-48 |

|         | 2.6.1     | Features                            | 2-48 |

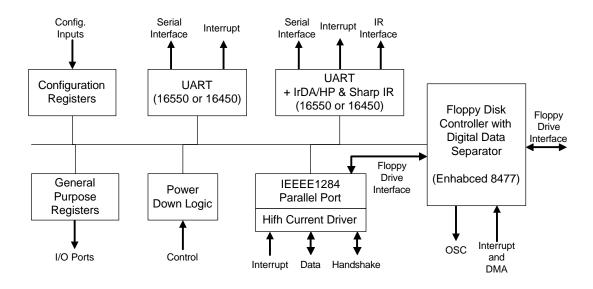

|         | 2.6.2     | Block Diagram                       | 2-50 |

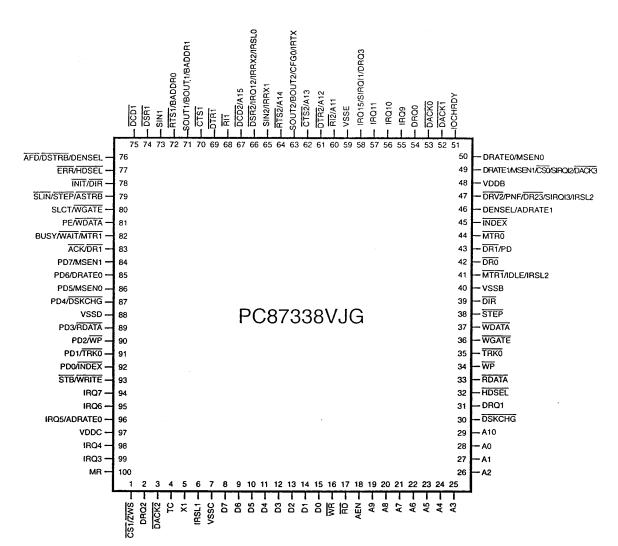

|         | 2.6.3     | Pin Diagram                         | 2-51 |

|         | 2.6.4     | Pin Description                     | 2-52 |

| 2.7     | CL-PD6    | 832: PCI-to-CardBus Host Adapter    | 2-59 |

|         | 2.7.1     | Features                            | 2-59 |

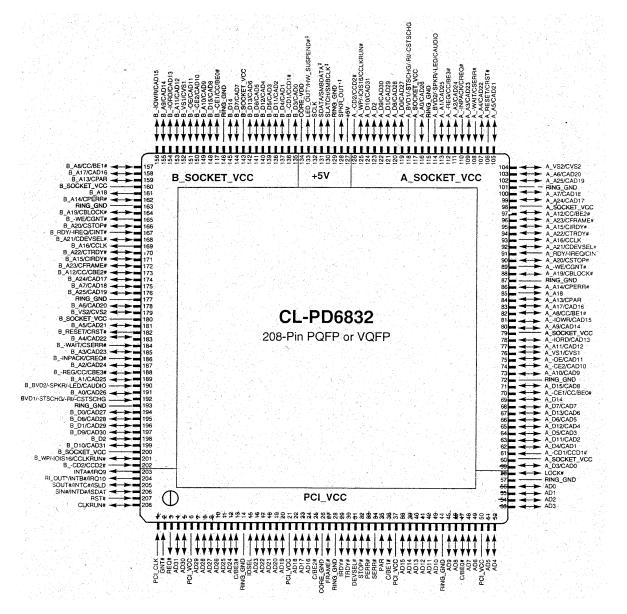

|         | 2.7.2     | Pin Diagram                         | 2-60 |

|         | 2.7.3     | Pin Descriptions                    | 2-60 |

| 2.8     | Ambit T   | 62.036.C DC-DC Converter            | 2-72 |

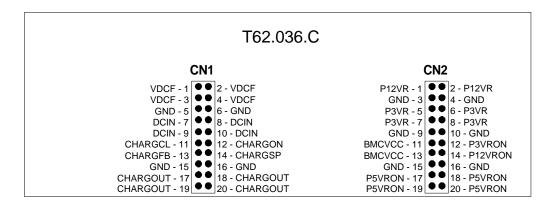

|         | 2.8.1     | Pin Diagram                         | 2-72 |

|         | 2.8.2     | Pin Descriptions                    | 2-72 |

| 2.9     | Ambit D   | C-AC Inverter                       | 2-74 |

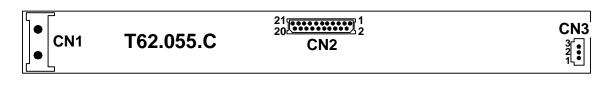

|         | 2.9.1     | T62.055C                            | 2-74 |

|         | 2.9.2     | T62.088C                            | 2-75 |

| Chapter | 3         | BIOS Setup Utility                  |      |

| 3.1     | About M   | ly Computer                         | 3-2  |

| 3.2     | System    | Configuration                       | 3-3  |

|         | 3.2.1     | Date and Time                       | 3-3  |

|         | 3.2.2     | Floppy Drives                       | 3-3  |

|         | 3.2.3     | Hard Disks                          | 3-3  |

|         | 3.2.4     | Num Lock After Boot                 | 3-3  |

|         | 3.2.5     | LCD Expansion Mode                  | 3-3  |

|         | 3.2.6     | Internal Speaker                    | 3-4  |

|         | 3.2.7     | Silent Boot                         | 3-4  |

Fast Boot ...... 3-

3.2.8

| 3.3 | Advance  | ed System Configuration             | 3-5  |

|-----|----------|-------------------------------------|------|

|     | 3.3.1    | Internal Cache                      | 3-5  |

|     | 3.3.2    | External Cache                      | 3-5  |

|     | 3.3.3    | Enhanced IDE Features               | 3-5  |

|     | 3.3.4    | Onboard Communication Ports         | 3-6  |

|     | 3.3.5    | Onboard USB                         | 3-6  |

|     | 3.3.6    | Reset PnP Resources                 | 3-7  |

| 3.4 | Power S  | Saving Options                      | 3-8  |

|     | 3.4.1    | When Lid is Closed                  | 3-8  |

|     | 3.4.2    | Suspend to Disk on Critical Battery | 3-8  |

|     | 3.4.3    | Display Always On                   | 3-8  |

|     | 3.4.4    | Resume On Modem Rings               | 3-8  |

|     | 3.4.5    | Resume On Schedule                  | 3-9  |

| 3.5 | System   | Security                            | 3-10 |

|     | 3.5.1    | Supervisor and User Passwords       | 3-10 |

|     | 3.5.2    | Diskette Drive Access Control       | 3-11 |

|     | 3.5.3    | Hard Disk Drive Access Control      | 3-11 |

|     | 3.5.4    | Start Up Sequences                  | 3-11 |

|     | 3.5.5    | Refresh New BIOS                    | 3-11 |

| 3.6 | Reset To | o Default Settings                  | 3-12 |

### Chapter 4 Disassembly and Unit Replacement

| 4.1 | General Information4-            |                      | 4-1  |

|-----|----------------------------------|----------------------|------|

|     | 4.1.1                            | Before You Begin     | 4-1  |

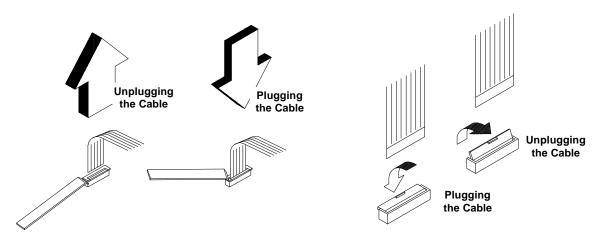

|     | 4.1.2                            | Connector Types      | 4-3  |

|     | 4.1.3                            | Disassembly Sequence | 4-4  |

| 4.2 | Removir                          | ng the Module        | 4-6  |

| 4.3 | Replacing the Hard Disk Drive4-7 |                      |      |

| 4.4 | Replacing Memory4-8              |                      |      |

| 4.5 | Removing the Keyboard4-10        |                      | 4-10 |

| 4.6 | Replacing the CPU4-12            |                      | 4-12 |

| 4.7 | Removing the Display4-1          |                      | 4-13 |

| 4.8 | Disassembling the Housing4-14    |                      | 4-14 |

|     | 4.8.1    | Detaching the Lower Housing from the Inside Assembly | .4-14 |

|-----|----------|------------------------------------------------------|-------|

|     | 4.8.2    | Detaching the Upper Housing from the Inside Assembly | .4-15 |

|     | 4.8.3    | Removing the Touchpad                                | .4-16 |

|     | 4.8.4    | Removing the Main Board                              | .4-16 |

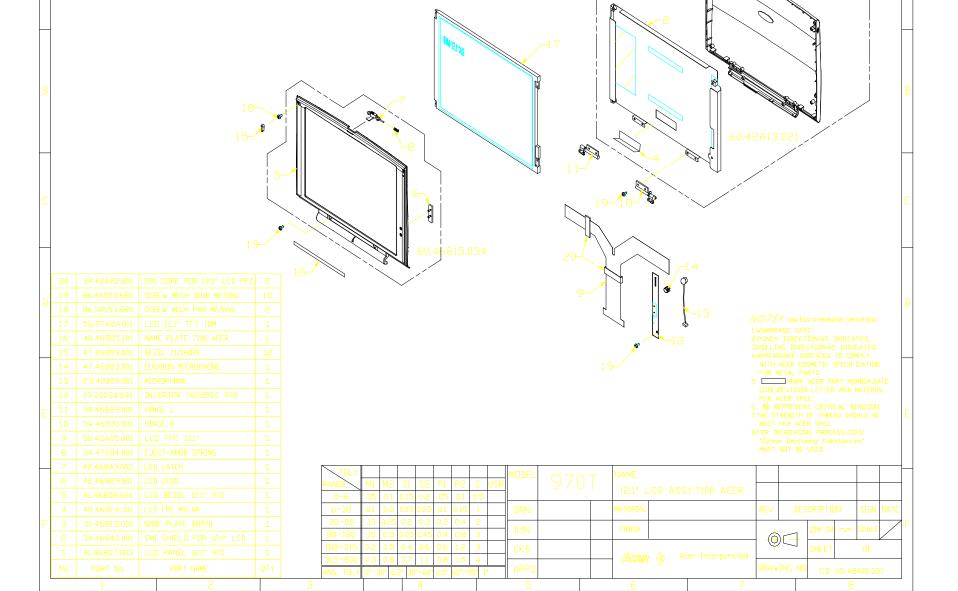

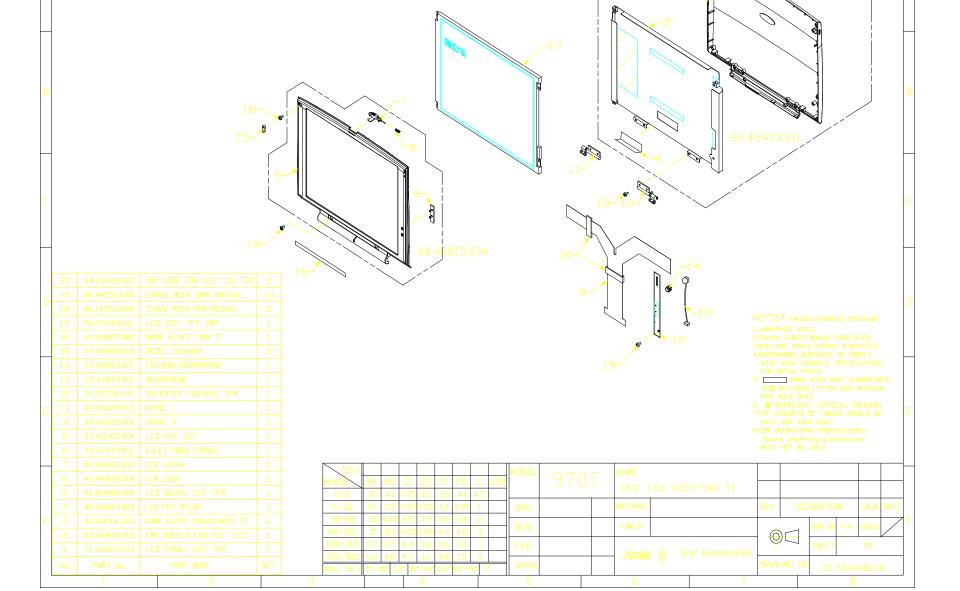

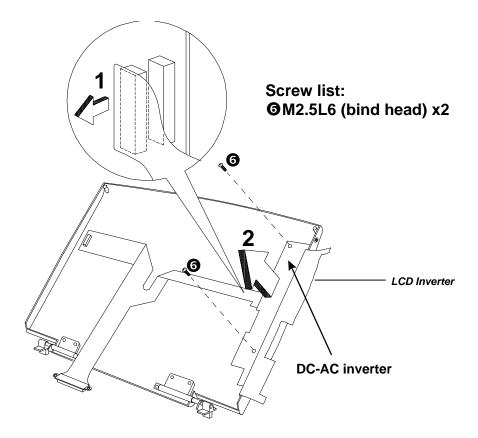

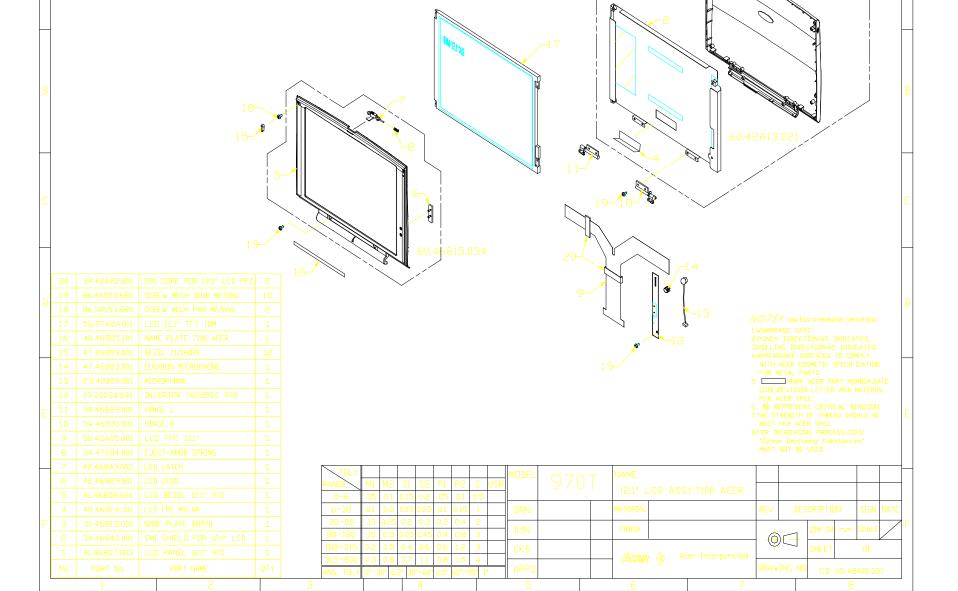

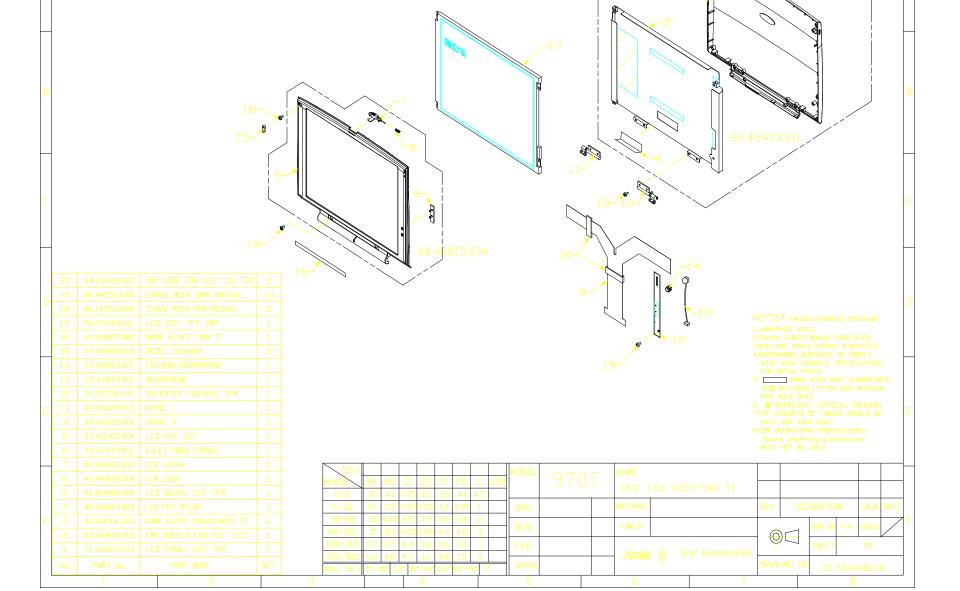

| 4.9 | Disasser | mbling the Display                                   | .4-19 |

### Appendices

- Appendix A Model Number Definition

- Appendix B Exploded View Diagram

- Appendix C Spare Parts List

- Appendix D Schematics

- Appendix E BIOS POST Checkpoints

### List of Figures

| 1-1  | Lid Switch                                       | 1-2  |

|------|--------------------------------------------------|------|

| 1-2  | Rear Port Location                               | 1-3  |

| 1-3  | Left Port Location                               | 1-4  |

| 1-4  | Indicator Lights                                 | 1-5  |

| 1-5  | System Board (Top Side)                          | 1-12 |

| 1-6  | System Board (Bottom Side)                       | 1-13 |

| 1-7  | Media Board (Top Side)                           | 1-14 |

| 1-8  | Media Board (Bottom Side)                        | 1-15 |

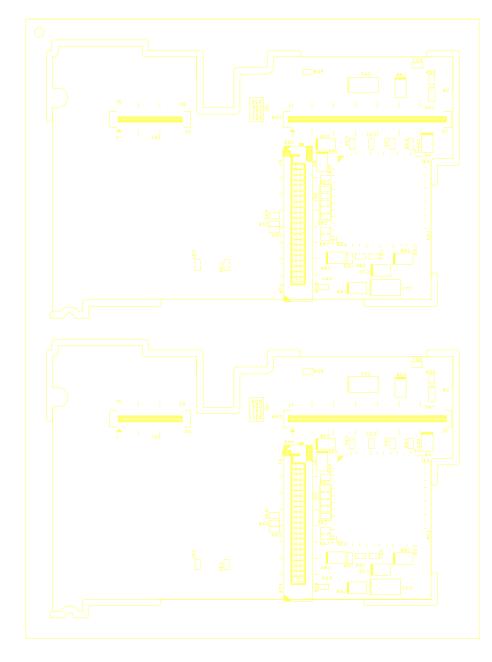

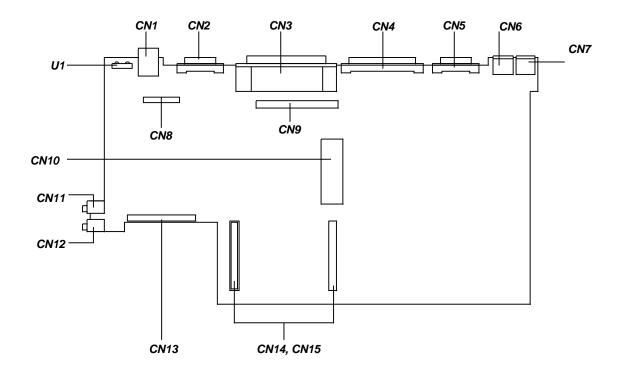

| 1-9  | Mainboard Jumpers and Connectors (Top Side)      | 1-16 |

| 1-10 | Mainboard Jumpers and Connectors (Bottom Side)   | 1-17 |

| 1-11 | Media Board Jumpers and Connectors (Top Side)    | 1-18 |

| 1-12 | Media Board Jumpers and Connectors (Bottom Side) | 1-18 |

| 1-13 | System Functional Block Diagram                  | 1-42 |

| 1-14 | System Bus Block Diagram                         | 1-43 |

| 2-1  | PIIX4 Architecture Block Diagram                 | 2-6  |

| 2-2  | PIIX4 Simplified Block Diagram                   | 2-7  |

| 2-3  | NM2160 Pin Diagram                               | 2-30 |

| 2-4  | NMA1 Block Diagram                               | 2-39 |

| 2-5  | NMA1 Pin Diagram                                 | 2-40 |

| 2-6  | 87C552 Block Diagram                             | 2-44 |

| 2-7  | 87C552 Pin Diagram                               | 2-45 |

| 2-8  | NS87338VJG Block Diagram                         | 2-50 |

| 2-9  | NS87338VJG Pin Diagram                           | 2-51 |

| 2-10 | CL-PD6832 Pin Diagram                            | 2-60 |

| 2-11 | T62.036.C Pin Diagram                            | 2-72 |

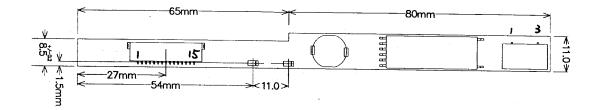

| 2-12 | T62.055.C Pin Diagram                            | 2-74 |

| 2-13 | T62.088.C Pin Diagram                            | 2-75 |

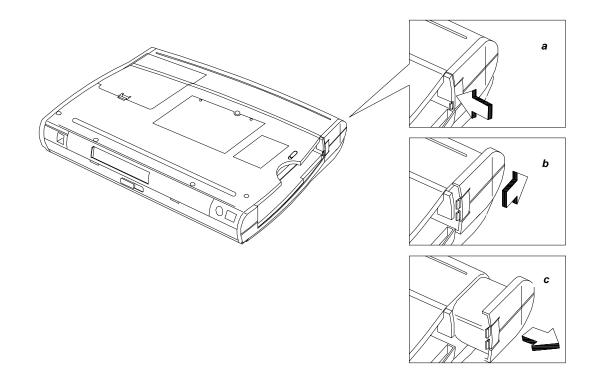

| 4-1  | Removing the Battery Pack                        | 4-2  |

| 4-2  | Using Plastic Stick on Connector With Locks      | 4-3  |

| 4-3  | Disassembly Flow                                 | 4-5  |

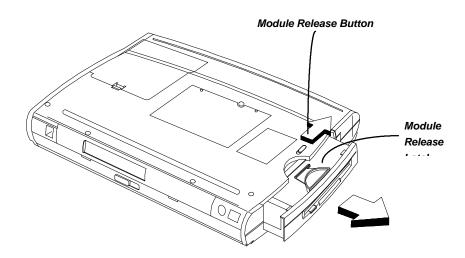

| 4-4  | Removing the Module                              | 4-6  |

| 4-5  | Removing the Hard Disk Drive Bay Cover           | 4-7  |

| 4-6  | Removing the Hard Disk Drive                     | 4-7  |

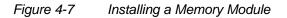

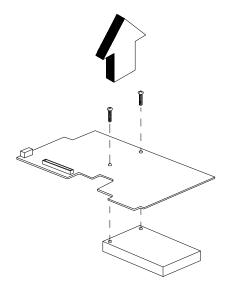

| 4-7  | Installing a Memory Module                       | 4-8  |

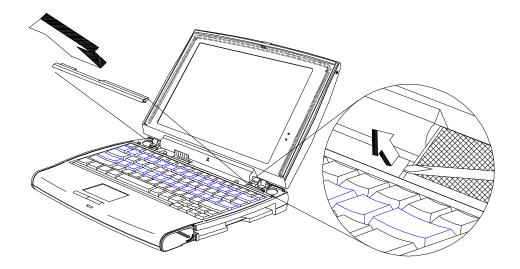

| 4-8  | Installing and Removing Memory                               | 4-8  |

|------|--------------------------------------------------------------|------|

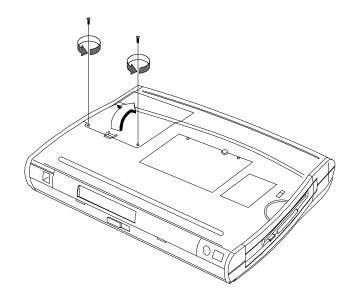

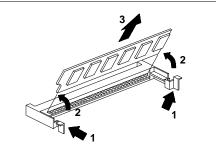

| 4-9  | Removing the Display Hinge Covers                            | 4-10 |

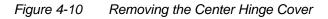

| 4-10 | Removing the Center Hinge Cover                              | 4-10 |

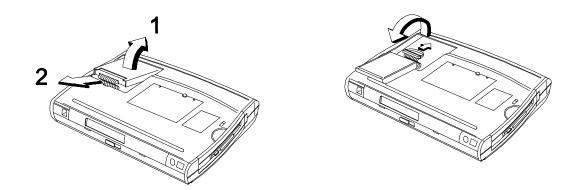

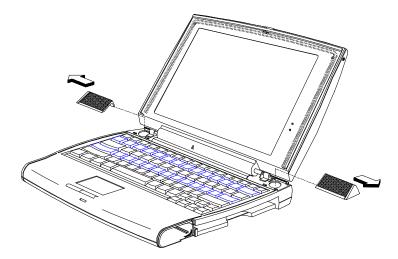

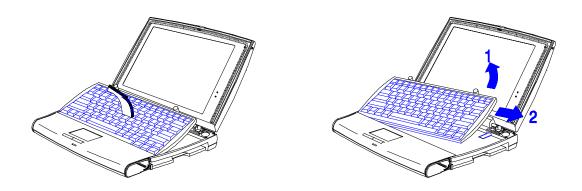

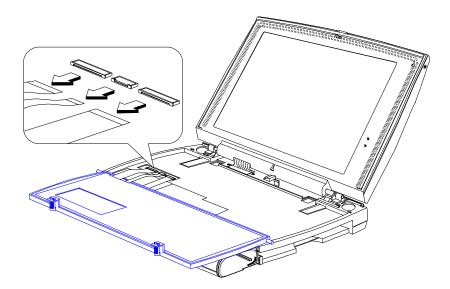

| 4-11 | Lifting Out the Keyboard                                     | 4-11 |

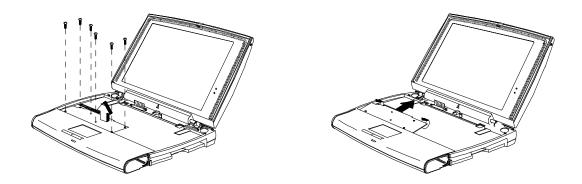

| 4-12 | Unplugging the Keyboard Connectors and Removing the Keyboard | 4-11 |

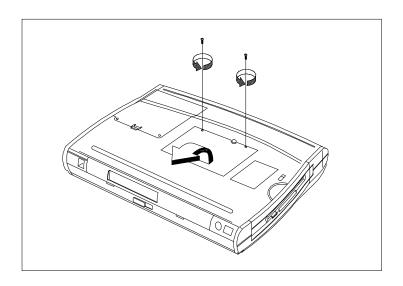

| 4-13 | Removing the CPU Heat Sink                                   | 4-12 |

| 4-14 | Removing the CPU Module                                      | 4-12 |

| 4-15 | Unplugging the Display Cable                                 | 4-13 |

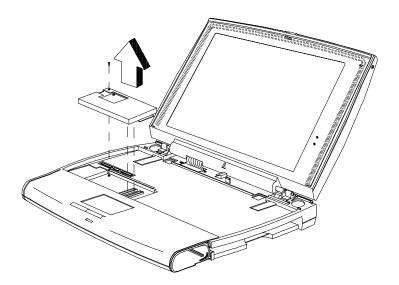

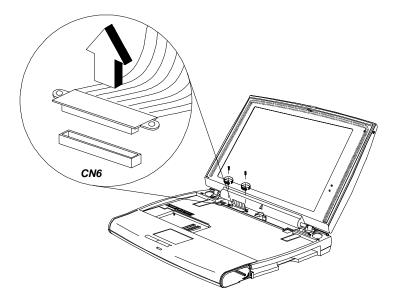

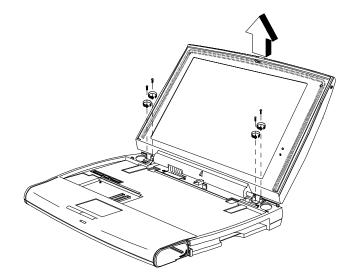

| 4-16 | Removing the Display Hinge Screws and Removing the Display   | 4-13 |

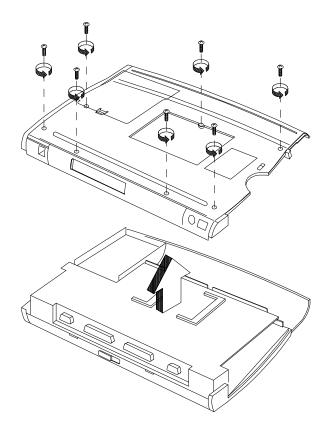

| 4-17 | Removing the Lower Housing                                   | 4-14 |

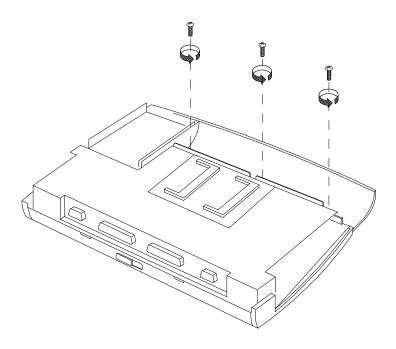

| 4-18 | Removing the Battery Bay Screws                              | 4-15 |

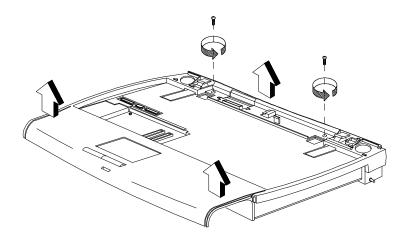

| 4-19 | Detaching the Upper Housing from the Inside Frame Assembly   | 4-15 |

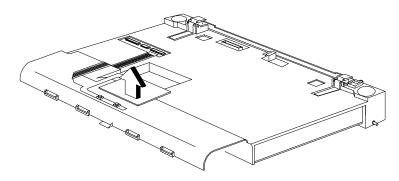

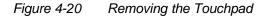

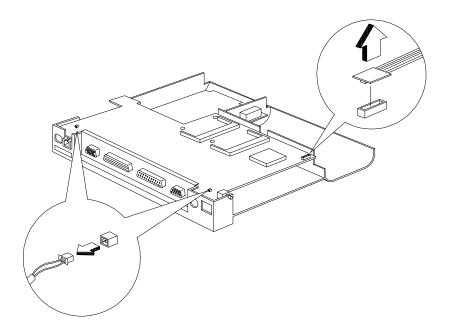

| 4-20 | Removing the Touchpad                                        | 4-16 |

| 4-21 | Unplugging the Speaker Connectors and Battery Pack Connector | 4-16 |

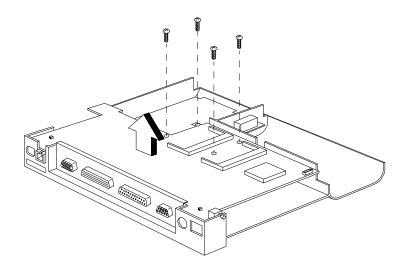

| 4-22 | Removing the Main Board                                      | 4-17 |

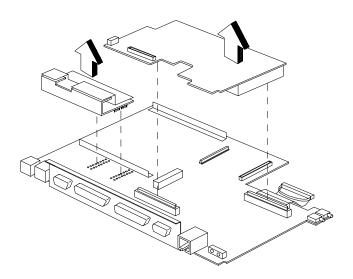

| 4-23 | Removing the Charger Board and Multimedia Board              | 4-17 |

| 4-24 | Removing the PC Card Slots                                   | 4-18 |

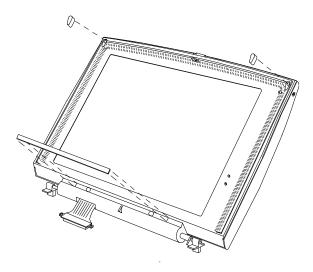

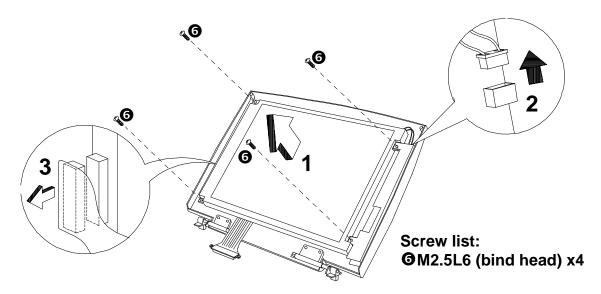

| 4-25 | Removing the LCD Bumpers                                     | 4-19 |

| 4-26 | Removing the Display Bezel Screws                            | 4-19 |

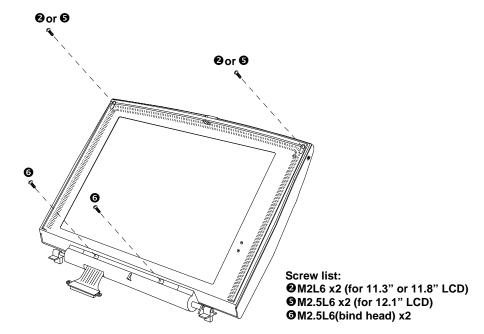

| 4-27 | Removing the Display Bezel                                   | 4-20 |

| 4-28 | Removing the Display Panel Screws and the Display Connectors | 4-20 |

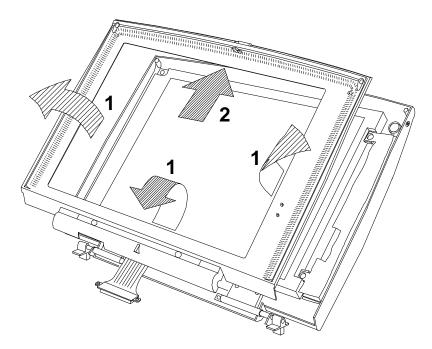

| 4-29 | Removing the Display Cable Assembly                          | 4-21 |

### List of Tables

| 1-1  | Rear Port Descriptions                        | 1-3  |

|------|-----------------------------------------------|------|

| 1-2  | Left Port Descriptions                        | 1-5  |

| 1-3  | Indicator Light Descriptions                  | 1-5  |

| 1-4  | Hot Key Descriptions                          | 1-6  |

| 1-5  | Eject Menu Item Descriptions                  | 1-7  |

| 1-6  | System Specifications                         | 1-9  |

| 1-7  | Mainboard Jumpers Pads Settings (Bottom Side) | 1-17 |

| 1-8  | System Memory Map                             | 1-19 |

| 1-9  | Interrupt Channel Map                         | 1-19 |

| 1-10 | I/O Address Map                               | 1-19 |

| 1-11 | DMA Channel Map                               | 1-20 |

| 1-12 | GPIO Port Definition Map I                    | 1-21 |

| 1-13 | GPIO Port Definition Map II                   | 1-22 |

| 1-14 | PCI Devices Assignment                        | 1-25 |

| 1-15 | PMU Timers List                               | 1-26 |

| 1-16 | CPU Module Specifications                     | 1-31 |

| 1-17 | BIOS Specifications                           | 1-32 |

| 1-18 | System Memory Specifications                  | 1-32 |

| 1-19 | SIMM Memory Combination List                  | 1-33 |

| 1-20 | Video Memory Specification                    | 1-33 |

| 1-21 | Video Display Specification                   | 1-34 |

| 1-22 | External CRT Resolution Modes                 | 1-34 |

| 1-23 | LCD Resolution Modes                          | 1-34 |

| 1-24 | Audio Specifications                          | 1-35 |

| 1-25 | PCMCIA Specifications                         | 1-35 |

| 1-26 | Parallel Port Specifications                  | 1-36 |

| 1-27 | Serial Port Specifications                    | 1-36 |

| 1-28 | Touchpad Specifications                       | 1-36 |

| 1-29 | SIR/FIR Specifications                        | 1-37 |

| 1-30 | LCD Specifications                            | 1-37 |

| 1-31 | CD-ROM Specifications                         | 1-38 |

| 1-32 | Diskette Drive Specifications                 | 1-38 |

| 1-33 | Hard Disk Drive Specifications                | 1-39 |

| 1-34 | Keyboard Specifications                       | 1-39 |

| 1-35 | Battery Specifications         | 1-40 |

|------|--------------------------------|------|

| 1-36 | DC-DC Converter Specifications | 1-40 |

| 1-37 | DC-AC Inverter Specifications  | 1-41 |

| 1-38 | AC Adapter Specifications      | 1-41 |

| 1-39 | Environmental Requirements     | 1-44 |

| 1-40 | Mechanical Specifications      | 1-45 |

| 2-1  | Major Chips List               | 2-1  |

| 2-2  | 82371AB Pin Descriptions       | 2-9  |

| 2-3  | NM2160 Pin Descriptions        | 2-31 |

| 2-4  | NMA1 Pin Descriptions          | 2-41 |

| 2-5  | 87C552 Pin Descriptions        | 2-46 |

| 2-6  | NS87338VJG Pin Descriptions    | 2-52 |

| 2-7  | CL-PD6832 Pin Descriptions     | 2-62 |

| 2-8  | T62.036.C Pin Descriptions     | 2-72 |

| 2-9  | T62.055.C Pin Descriptions     | 2-74 |

| 2-10 | T62.088.C Pin Descriptions     | 2-75 |

| 3-1  | About My Computer Parameters   | 3-2  |

| 3-2  | Start Up Sequences             | 3-11 |

| 4-1  | Guide to Disassembly Sequence  | 4-4  |

| B-1  | Exploded View Diagram List     | B-1  |

| C-1  | Spare Parts List               | C-1  |

| D-1  | Schematics Diagram List        | D-1  |

| E-1  | POST Checkpoint List           | E-1  |

## Chapter

# 1

# System Introduction

The computer is packed with features that make it as easy to work with as it is to look at. Here are some of the computer's features:

### 1.1 Features

#### PERFORMANCE

- Intel Pentium<sup>®</sup> processor with MMX<sup>™</sup> technology

- 64-bit main memory and 512KB external (L2) cache memory

- Large display in active-matrix TFT

- PCI local bus video with 128-bit graphics accelerator

- Flexible module bay (3.5-inch floppy drive or CD-ROM drive or second hard disk drive option)

- High-capacity, Enhanced-IDE hard disk

- An advanced power management system with two power-saving modes

- Lithium-Ion smart battery pack

- High-speed connectivity

#### MULTIMEDIA AND COMMUNICATIONS

- 16-bit stereo audio with built-in FM synthesizer and 3D sound effect

- Built-in microphone and dual angled stereo speakers

- Support for simultaneous display on the built-in screen and an external monitor for presentations

- Full-screen, 30 frames per second, true-color MPEG video playback

- Infrared wireless communication

#### ERGONOMICS

- Intuitive FlashStart automatic power-on

- Sleek, smooth and stylish design

- Automatic tilt-up (12.1-inch models only), full-sized, full-function keyboard

- Wide and comfortable palm rest

• Ergonomically-positioned touchpad pointing device

#### EXPANDABILITY

- CardBus PC Card (PCMCIA) slots (two type II/I or one type III) with Zoomed Video port function

- Mini-dock option with two CardBus PC Card slots (two type II/I or one type III)

- USB port onboard

- Upgradeable memory and hard disk

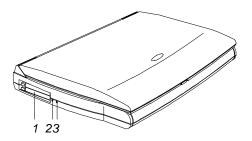

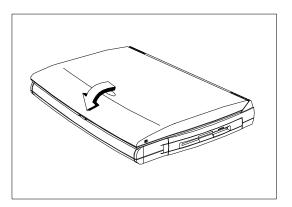

### 1.1.2 FlashStart Automatic Power-On

The computer has no on/off switch. Instead it uses a lid switch, located near the center of the display hinge, that turns the computer on and off automatically.

#### Figure 1-1 Lid Switch

When you close the display lid, the computer saves all data either to the hard disk or to memory, depending on the When Lid Is Closed setting (see section 3.4.1). When all data is saved, the computer turns itself off. When you reopen the lid, the computer retrieves your data and resumes where you left off.

### 1.2 Ports

The computer's ports allow you to connect peripheral devices to your computer just as you would to a desktop PC. The main ports are found on the computer's rear panel. The computer's left panel contains the computer's multimedia ports and PC card slots.

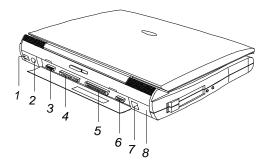

### 1.2.1 Rear Panel Ports

The computer's rear panel contains the computer's main ports and connectors as shown in the illustration below.

- 1 DC-in Port

- 2 PS/2 Port

- 3 Serial Port

- 4 Parallel Port

- 5 Mini Dock Connector

- 6 External CRT Port

- 7 USB Port

- 8 Infrared Port

Figure 1-2 Rear Port Location

Table 1-1 Rear Port Descriptions

| Port                                  | lcon | Connects to                                                                                |

|---------------------------------------|------|--------------------------------------------------------------------------------------------|

| DC-in port                            |      | AC adapter and power outlet                                                                |

| PS/2 port                             | Ð    | PS/2-compatible device<br>(PS/2 keyboard, keypad, mouse)                                   |

| Serial port<br>(UART16650-compatible) | [00] | Serial device (serial mouse)                                                               |

| Parallel port (EPP/ECP-<br>compliant) | l    | Parallel device (parallel printer, external floppy drive)                                  |

| Mini dock connector                   |      | Mini dock                                                                                  |

| External CRT port                     |      | External monitor (up to 1024x768x256 colors)                                               |

| USB port                              | Q    | USB device (USB mouse, keyboard)                                                           |

| Infrared port                         |      | Infrared-aware device (computer with IR port, desktop with IR adapter, IR-capable printer) |

#### UNIVERSAL SERIAL BUS (USB) PORT

The computer's USB (Universal Serial Bus) port located on the rear panel allows you to connect peripherals without occupying too many resources. Common USB devices include the mouse and keyboard.

#### FAST INFRARED (FIR) PORT

The computer's FIR (fast infrared) port located on the rear panel allows you to transfer data to IRaware machines without cables. For example, you can transfer data between two IR-capable computers, or send data to an IR-aware printer without using a cable.

The infrared port is IrDA-compliant, and can transfer data at speeds of up to 4 megabits per second (Mbps) at a distance of up to one meter.

To use the infrared port, position two IR-aware devices such that their IR ports are no more than one meter apart and offset no more than 15 degrees.

When the two computers are in position, simply begin the data transfer as you normally would. See your file transfer software for details.

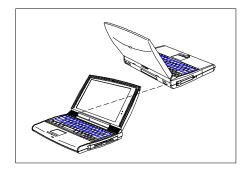

#### 1.2.2 Left Panel Ports

The computer's left side panel contains the computer's multimedia ports and PC card slots, as shown in the illustration on the next page.

1 PC Card Slots

- 2 Microphone-in/Line-in Port

- 3 Speaker-out/Line-out Port

Figure 1-3 Left Port Location

#### Table 1-2Left Port Descriptions

| Port                   | lcon              | Connects to                                 |

|------------------------|-------------------|---------------------------------------------|

| PC Card slots          |                   | Two type I/II PC Cards or one type III Card |

| Microphone-in/ Line-in | ( <del>**)</del>  | External microphone or line input device    |

| Speaker-out/ Line-out  | (( <del>*))</del> | Amplified speakers or headphones            |

#### PC CARD SLOTS

The computer contains two PC card slots on the left panel that accommodate two type I/II or one type III PC card(s). Consult your dealer for available PC card options.

#### MULTIMEDIA PORTS

The computer provides a Mic-In/Line-in port and a Speaker-out/Line-out port on the left panel to accommodate multimedia audio devices, such as a microphone, speakers, or headphones.

### 1.2.3 Indicator Lights

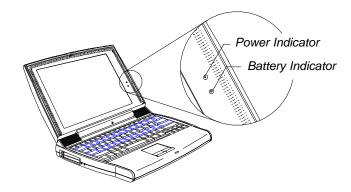

The display panel contains a power indicator light and a battery indicator light as shown in the illustration below.

Figure 1-4 Indicator Lights

Table 1-3 Indicator Light Descriptions

| Indicator Light   | lcon | Description                                                                         |

|-------------------|------|-------------------------------------------------------------------------------------|

| Power Indicator   | ዑ    | Lights when power is on.<br>Flashes when the computer is in suspend-to-memory mode. |

| Battery Indicator | D    | Lights when the battery pack is charging.<br>Flashes when battery power is low.     |

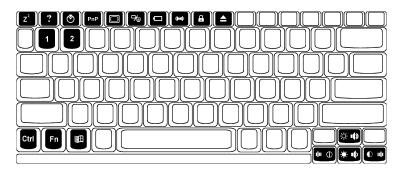

### 1.2.4 Hot Keys

The computer's special Fn key, used in combination with other keys, provides "hot-key" combinations that access system control functions, such as screen contrast, brightness, volume output, and the BIOS setup utility.

Table 1-4Hot Key Descriptions

| Hot Key   | lcon           | Function                                    | Description                                                                                                                                                             |

|-----------|----------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fn+Esc    | Z <sup>z</sup> | Suspend-to-memory                           | Enters suspend-to-memory mode                                                                                                                                           |

| Fn+F1     | ?              | Help                                        | Displays the hot-key list                                                                                                                                               |

| Fn+F2     | ٢              | Setup                                       | Enters the BIOS setup utility                                                                                                                                           |

| Fn+F3     | PnP            | Plug and Play<br>Configuration              | Performs system configuration for Plug and Play operating systems like Windows 95                                                                                       |

| Fn+F4     |                | Screen Blackout                             | Blanks the screen to save power; to wake up the screen, press any key                                                                                                   |

| Fn+F5     |                | Display Toggle                              | Switches display from the built-in display, to an external monitor, to both built-in and external if one is connected                                                   |

| Fn+F6     | 0              | Fuel Gauge On/Off                           | Toggles battery gauge display on and off. The gauge shows the percentage of charge left in the battery.                                                                 |

|           |                |                                             | Shows a plug icon if a powered AC adapter is connected to the computer; shows a speaker icon if speaker output is on (Fn+F7); shows a T icon if turbo mode is on (Fn+2) |

| Fn+F7     | <b>J</b> III() | Speaker On/Off                              | Toggles speaker output on and off                                                                                                                                       |

| Fn+F8     | •              | Lock System<br>Resources<br>(Password Lock) | Locks the computer and requires a password to unlock it                                                                                                                 |

| Fn+F9     |                | Eject                                       | Accesses the eject menu described on page 7                                                                                                                             |

| Fn+Ctrl+↑ | •())           | Volume Up                                   | Increases speaker volume                                                                                                                                                |

| Fn+Ctrl+↓ | Þ              | Volume Down                                 | Decreases speaker volume                                                                                                                                                |

| Fn+Ctrl+→ | ı              | Balance Right                               | Shifts speaker balance to the right                                                                                                                                     |

| Fn+Ctrl+← | ı <b>l</b> ıı  | Balance Left                                | Shifts speaker balance to the left                                                                                                                                      |

#### Table 1-4Hot Key Descriptions

| Hot Key | lcon | Function          | Description                                                |

|---------|------|-------------------|------------------------------------------------------------|

| Fn+ı≇+↑ | ò    | Brightness Up     | Increases screen brightness                                |

| Fn+:≇+↓ | ۲    | Brightness Down   | Decreases screen brightness                                |

| Fn+∄+→  | 0    | Contrast Up       | Increases screen contrast (not available for TFT displays) |

| Fn+∄≇+← | Φ    | Contrast Down     | Decreases screen contrast (not available for TFT displays) |

| Fn+↑    |      | Fuel Gauge Up     | With the fuel gauge displayed, moves the fuel gauge up     |

| Fn+↓    |      | Fuel Gauge Down   | With the fuel gauge displayed, moves the fuel gauge down   |

| Fn+→    |      | Fuel Gauge Right  | With the fuel gauge displayed, moves the fuel gauge right  |

| Fn+←    |      | Fuel Gauge Left   | With the fuel gauge displayed, moves the fuel gauge left   |

| Fn+1    |      | CD Eject          | Ejects the CD-ROM drive                                    |

| Fn+2    |      | Turbo Mode On/Off | Toggles turbo mode on and off                              |

#### EJECT MENU

The Fn+F9 hot-key combination brings up a special eject menu that allows you to perform several system configuration functions.

Eject Options: Battery (Suspend-to-disk) .....Change CD-ROM Disk (Also Fn-1) .....Eject Mini Dock (Suspend) ....Change Power Off ....Change ↑↓←→ = Move Highlight Bar, ↓ = Select, ESC = Exit

#### Table 1-5 Eject Menu Item Descriptions

| Select                       | То                                                                                                                                                                                                                |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Battery<br>(Suspend to Disk) | Store all current data and system information to the hard disk.                                                                                                                                                   |

| CD-ROM Disk<br>(Also Fn-1)   | Open the CD-ROM drive (eject a CD).                                                                                                                                                                               |

| Mini Dock<br>(Suspend)       | Undock the computer. Press the dock lock and pull the dock handle toward you to undock the computer. (See the mini dock manual for details.) Once the computer is successfully undocked, press any key to resume. |

| Power Off                    | Turn the computer off. If you are using Windows 95, use the Shutdown command to turn off your computer.                                                                                                           |

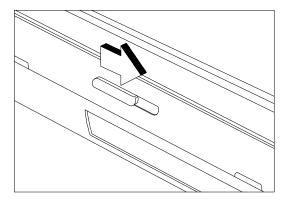

### 1.2.5 Automatic Tilt

The computer (models with 12.1-inch LCDs) can automatically tilt the keyboard to a six-degree angle whenever you open the lid to provide a comfortable typing angle similar to desktop keyboards.

To set the automatic tilt feature, follow these steps:

1. Close the lid.

2. To enable the automatic tilt feature, slide the tilt switch, located above the port cover on the rear of the computer, to the right.

To disable the automatic tilt feature, slide the tilt switch to the left.

3. Open the lid.

# **1.3 System Specification Overview**

### Table 1-6System Specifications

| Item                         | Standard                                                                                                | Optional                                                                               |

|------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Microprocessor               | Intel Pentium <sup>®</sup> processor with MMX™<br>technology                                            |                                                                                        |

| Memory<br>System / Main      | 32MB<br>Dual 64-bit memory banks                                                                        | Expandable to 128MB using<br>8/16/32/64MB soDIMMs                                      |

| External cache               | 512KB L2 cache (synchronous SRAM)                                                                       |                                                                                        |

| Flash BIOS                   | 256KB                                                                                                   |                                                                                        |

| Storage system               | One 2.5-inch, high-capacity Enhanced-IDE<br>hard disk                                                   | Higher-capacity E-IDE hard disk                                                        |

|                              | One high-speed IDE CD-ROM drive module                                                                  | Second optional hard disk drive module (3-inch)                                        |

|                              | One 3.5-inch, 1.44MB floppy drive module (internal/external use)                                        |                                                                                        |

| Display                      | Active-matrix TFT LCD<br>12.1-inch, 800x600, 64K colors (SVGA)<br>13.3-inch, 1024x768, 64K colors (XGA) | Up to 1024x768, 256-color ultra-VGA monitor                                            |

|                              |                                                                                                         | LCD projection panel                                                                   |

| Video system                 | PCI local bus video with 128-bit graphics accelerator                                                   |                                                                                        |

| Audio system                 | 16-bit stereo audio with built-in FM synthesizer                                                        |                                                                                        |

|                              | Built-in microphone and dual angled speakers                                                            |                                                                                        |

| Communications system        |                                                                                                         | PC card modem                                                                          |

| Operating<br>system          | Windows 95                                                                                              |                                                                                        |

| Keyboard and pointing device | 84-/85-key with Win95 keys;<br>auto-tilt feature                                                        | 101-/102-key, PS/2-compatible<br>keyboard or 17-key numeric keypad                     |

|                              | Touchpad (centrally-located on palm rest)                                                               | External serial or PS/2 mouse or<br>similar pointing device                            |

| I/O ports                    | One 9-pin RS-232 serial port<br>(UART16550-compatible)                                                  | Serial mouse, printer or other serial devices                                          |

|                              | One 25-pin parallel port<br>(EPP/ECP-compliant)                                                         | Parallel printer or other parallel devices; floppy drive module (when used externally) |

|                              | One 15-pin CRT port                                                                                     | Up to a 1024x768 ultra-VGA monitor                                                     |

|                              | One 6-pin PS/2 connector                                                                                | 17-key numeric keypad, PS/2<br>keyboard, mouse or trackball                            |

|                              | One 240-pin mini dock connector                                                                         | Mini dock                                                                              |

### Table 1-6System Specifications

| ltem                                          | Standard                                                                      | Optional                     |

|-----------------------------------------------|-------------------------------------------------------------------------------|------------------------------|

| I/O Ports<br>(continued)                      | One type III or two type II PC Card slot(s)                                   | LAN card or other PC cards   |

| (continued)                                   | One fast infrared port (IrDA-compliant)                                       | External IR adapter          |

|                                               | One 3.5mm minijack microphone-in/line-in<br>jack                              | Microphone or line-in device |

|                                               | One 3.5mm minijack speaker-out/line-out<br>jack                               | Speakers or headphones       |

|                                               | One USB port                                                                  | USB device                   |

| Weight<br>with FDD<br>with CD-ROM             | (includes battery)<br>3.4 kg. (7.4 lbs.)<br>3.5 kg. (7.5 lbs.)                |                              |

| Dimensions<br>Round contour<br>Main footprint | L x W x H<br>309x240x56mm<br>12.2" x 9.5" x 2.2"                              | Carrying bag                 |

| Temperature<br>Operating<br>Non-operating     | 10°C ~ 35°C(50°F ~ 95°F)<br>-10°C ~ 60°C(14°F ~ 140°F)                        |                              |

| Humidity<br>Operating<br>Non-operating        | (non-condensing)<br>20% ~ 80% RH<br>20% ~ 80% RH                              |                              |

| AC adapter                                    | 100~240Vac, 50~60Hz autosensing AC adapter                                    | Extra AC adapter             |

| Battery pack<br>Type                          | 57WH Lithium-Ion battery with intelligent charging and built-in battery gauge | Extra battery pack           |

| Charge time                                   | 2.0-hour rapid-charge<br>4.0-hour in-use charge                               |                              |

# 1.4 Board Layout

1.4.2 System Board (Bottom Side)

1.4.3 Media Board (Top Side)

Figure 1-7 Media Board (Top Side)

### 1.4.4 Media Board (Bottom Side)

## 1.5 Jumpers and Connectors

### 1.5.1 Mainboard

| CN1 | USB                     | CN8, CN9   | Multimedia board connector |

|-----|-------------------------|------------|----------------------------|

| CN2 | VGA port                | CN10       | FDD/CD-ROM connector       |

| CN3 | Mini dock port          | CN14, CN15 | CPU board connector        |

| CN4 | Parallel port           | CN13       | Hard disk drive connector  |

| CN5 | Serial Port             | CN12       | Speaker-out/Line-out Jack  |

| CN6 | PS2 mouse/keyboard port | CN11       | Microphone-in/Line-in Jack |

| CN7 | AC adapter plug-in port | U1         | SIR/FIR infrared LED       |

Figure 1-9 Mainboard Jumpers and Connectors (Top Side)

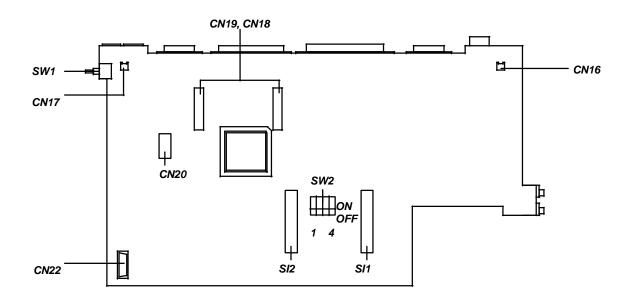

| CN20, CN19 | DC-DC converter connector | CN22 | Battery connector       |

|------------|---------------------------|------|-------------------------|

| CN17       | Left speaker connector    | CN16 | Right speaker connector |

| CN20       | Debug port                | SW1  | Reset Switch            |

|            |                           | SW2  | Jumper Setting          |

Figure 1-10 Mainboard Jumpers and Connectors (Bottom Side)

The following table shows the settings of the mainboard's bottom side jumper pads.

| Table 1-7 | Mainboard Jumpers | Pads Settings | (Bottom Side) |

|-----------|-------------------|---------------|---------------|

|           |                   |               |               |

| Jumper Pad | Descriptions            | Settings                                    |

|------------|-------------------------|---------------------------------------------|

| SW2(1)     | Keyboard type selection | OFF: Other keyboard<br>ON: Japan keyboard   |

| SW2(2)     | Password settings       | OFF: Enable password<br>ON: Bypass password |

| SW2(3)     | BIOS type selection     | OFF: Acer BIOS<br>ON: OEM BIOS              |

| SW2(4)     | Reserved                |                                             |

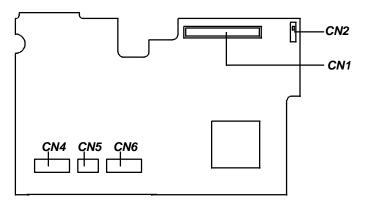

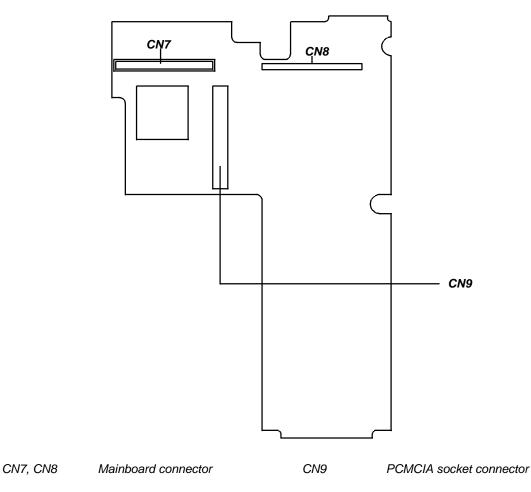

### 1.5.2 Media Board

CN2Lid switchCN6Touchpad connectorCN1LCD connectorCN4, CN5Keyboard connector

Figure 1-11 Media Board Jumpers and Connectors (Top Side)

*Figure 1-12 Media Board Jumpers and Connectors (Bottom Side)*

### **1.6** System Configurations and Specifications

### 1.6.1 System Memory Map

#### Table 1-8 System Memory Map

| Address Range                    | Definition                          | Function                                      |

|----------------------------------|-------------------------------------|-----------------------------------------------|

| 000000 -09FFFF                   | 640 KB memory                       | Base memory                                   |

| 0A0000 -0BFFFF                   | 128 KB video RAM                    | Reserved for graphics display buffer          |

| 0C0000 -0CBFFF                   | Video BIOS                          | Video BIOS                                    |

| 0CC000 -0CDFFF<br>0CE000 -0CFFFF | System CardBus<br>Mini dock CardBus |                                               |

| 0F0000 -0FFFFF                   | 64 KB system BIOS                   | System BIOS                                   |

| 010000 -07FFFF<br>080000 -027FFF | Extended memory                     | Onboard memory<br>SIMM memory                 |

| FE0000 -FFFFFF                   | 256 KB system ROM                   | Duplicate of code assignment at 0E0000-0FFFFF |

### 1.6.2 Interrupt Channel Map

### Table 1-9Interrupt Channel Map

| Interrupt Number | Interrupt Source (Device Name)             |  |  |  |

|------------------|--------------------------------------------|--|--|--|

| IRQ 0            | System Timer                               |  |  |  |

| IRQ 1            | Keyboard                                   |  |  |  |

| IRQ 2            | Cascade                                    |  |  |  |

| IRQ 3            | IrDA / 2F8h                                |  |  |  |

| IRQ 4            | Serial Port 1 / 3F8h                       |  |  |  |

| IRQ 5            | Audio                                      |  |  |  |

| IRQ 6            | Floppy Disk Controller (FDC)               |  |  |  |

| IRQ 7            | Parallel Port                              |  |  |  |

| IRQ 8            | Real Time Clock (RTC)                      |  |  |  |

| IRQ 9            | USB/System CardBus                         |  |  |  |

| IRQ 10           | Reserved for PCMCIA card                   |  |  |  |

| IRQ 11           | Reserved for PCMCIA card/Mini dock CardBus |  |  |  |

| IRQ 12           | PS/2 Mouse                                 |  |  |  |

| IRQ 13           | Co-processor                               |  |  |  |

| IRQ 14           | Hard disk                                  |  |  |  |

| IRQ 15           | CD-ROM                                     |  |  |  |

### 1.6.3 I/O Address Map

Table 1-10 I/O Address Map

| Address Range | Device                        |

|---------------|-------------------------------|

| 000 -00F      | DMA controller-1              |

| 020 -021      | Interrupt controller-1        |

| 02E -02F      | NS87338 peripheral controller |

| 040 -043      | Timer 1                       |

| 048 -04B      | Timer 2                       |

### Table 1-10 I/O Address Map

| Address Range | Device                          |

|---------------|---------------------------------|

| 060 -06E      | Keyboard controller chip select |

| 070 -071      | Real-time clock and NMI mask    |

| 080 -08F      | DMA page register               |

| 0A0 -0A1      | Interrupt controller-2          |

| 0C0 -0DF      | DMA controller-2                |

| 1F0 -1F7      | Hard disk select                |

| 3F6 -3F7      | Hard disk select                |

| 170 -177      | CD-ROM select                   |

| 376 -377      | CD-ROM select                   |

| 220 -22F      | Audio                           |

| 240 -24F      | Audio -default                  |

| 260 -26F      | Audio                           |

| 280 -28F      | Audio                           |

| 278 -27F      | Parallel port 3                 |

| 2E8 -2EF      | COM 4                           |

| 2F8 -2FF      | COM 2 -IrDA                     |

| 300 -301      | MPU-401 port -default           |

| 310 -311      | MPU-401 port                    |

| 320 -321      | MPU-401 port                    |

| 330 -321      | MPU-401 port                    |

| 378 -37F      | Parallel port 2                 |

| 388 -38B      | FM synthesizer                  |

| 3BC -3BE      | Parallel port 1                 |

| 3B4, 3B5, 3BA | Video subsystem                 |

| 3C0 -3C5      |                                 |

| 3C6 -3C9      | Video DAC                       |

| 3C0 -3CF      | Enhanced graphics display       |

| 3D0 -3DF      | Color graphics adapter          |

| 3E8 -3EF      | COM3                            |

| 3F0 -3F7      | Floppy disk controller          |

| 3F8 -3FF      | COM 1 -Serial 1                 |

| CF8 -CFF      | PCI configuration register      |

### 1.6.4 DMA Channel Map

| Table 1-11 | DMA Channel Map |

|------------|-----------------|

|------------|-----------------|

| Controller | Channel | Address | Function                                        |

|------------|---------|---------|-------------------------------------------------|

| 1          | 0       | 0087    | Audio(default) / IrDA(option)                   |

| 1          | 1       | 0083    | Audio(default) / ECP(option) / IrDA(option)     |

| 1          | 2       | 0081    | Diskette                                        |

| 1          | 3       | 0082    | Audio (option) / FIR IrDA(option) / ECP(option) |

| 2          | 4       | Cascade | Cascade                                         |

| 2          | 5       | 008B    |                                                 |

| 2          | 6       | 0089    | Spare                                           |

| 2          | 7       | 008A    |                                                 |

### 1.6.5 GPIO Port Definition Map

#### Table 1-12 GPIO Port Definition Map I

| GPIO/Signal                         | Pin # | I/O | Description                                                                                                                                                              |

|-------------------------------------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO Pin Assignment: PIIX4          |       |     |                                                                                                                                                                          |

| SUSA# (PX3_SUSA#)                   | W20   | 0   | 0: Power down clock generator                                                                                                                                            |

| GPO0 (PX3_DOCKRST#)                 | G4    | 0   | 0 : Enable docking reset                                                                                                                                                 |

| GPO1 (PX3_HDPON)                    | Y15   | 0   | 1: Turn on HDD power                                                                                                                                                     |

| GPO2 (PX3_ CD/FDPON)                | T14   | 0   | 1: Turn on CD/FDD power                                                                                                                                                  |

| GPO3 (PX3_ HDRST#)                  | W14   | 0   | 0: Reset HDD interface                                                                                                                                                   |

| GPO4 (PX3_CDRST#)                   | U13   | 0   | 0: Reset CD interface                                                                                                                                                    |

| GPO5 (PX3_3MODE)                    | V13   | 0   | 0: 3 mode drive                                                                                                                                                          |

| GPO6 (PX3_SMBSEL0)                  | Y13   | 0   | Select one of three SM buses                                                                                                                                             |

| GPO7 (PX3_SMBSEL1)                  | T12   | 0   | SMBSEL1 SMBSEL0                                                                                                                                                          |

|                                     |       |     | 00DRAM bank 0 SMB01DRAM bank 1 SMB10MMO LM75 & clock gen. SMB11PCMCIA LM75                                                                                               |

| GPO8 (PX3_DOCKGNT#)                 | T19   | 0   | 0: Granted docking                                                                                                                                                       |

| GPO9/GNTA# (PX3_VDPD)               | N1    | 0   | 1: Power down VGA                                                                                                                                                        |

| GPO10/GNTB# (PX3_VGADIS)            | P2    | 0   | 1: Disable VGA from PCI                                                                                                                                                  |

| GPO11/GNTC# (PX3_AUDPON)            | P4    | 0   | 1: Power on analog audio power                                                                                                                                           |

| GPO12/APICACK#                      | J17   | 0   | NC                                                                                                                                                                       |

| GPO13/APICCS#                       | H18   | 0   | NC                                                                                                                                                                       |

| GPO14/IRQ0 (PX3_ROM#)               | H20   | 0   | 0: Enable ROMCS#                                                                                                                                                         |

| GPO15/SUSB#                         | V19   | 0   | NC                                                                                                                                                                       |

| GPO16/SUSC#                         | U18   | 0   | NC                                                                                                                                                                       |

| GPO17/CPU_STP#(PX3_CPUSTP#)         | R1    | 0   | 0: Enable CPU clock stop                                                                                                                                                 |

| GPO18/PCI_STP# (PX3_PCISTP#)        | R2    | 0   | 0: Enable PCI clock stop                                                                                                                                                 |

| GPO19/ZZ (PXI_L2ZZ)                 | K16   | 0   | 1: Power down L2 cache                                                                                                                                                   |

| GPO20/SUS_STAT1#(PX3_SUSTAT#)       | T17   | 0   | 0: Enable MTXC power down                                                                                                                                                |

| GPO21/SUS_STAT2#<br>(PM3_A_ACT/PD#) | T18   | 0   | 0: Power down PD6832 Cardbus controller                                                                                                                                  |

| GPO22/XDIR# (PX3_FDDBEN)            | M3    | 0   | 1: FDD buffer enable                                                                                                                                                     |

| GPO23/XOE# (PX3_SPPD)               | M4    | 0   | 1: Power down serial interface                                                                                                                                           |

| GPO27 (PX3_SPKOFF)                  | G5    | 0   | 1: Turn off speaker                                                                                                                                                      |

| GPO28 (PX3_FLASHVPP)                | F2    | 0   | 1: Enable Flash Vpp control                                                                                                                                              |

| GPO29 (PX3_FPAGE1)                  | F3    | 0   | Force BIOS to high page 1F segment and 3 E segments                                                                                                                      |

| GPO30 (PX3_FPAGE2)                  | F4    | 0   | FPAGE2         FPAGE1           0         0         F, E0           0         1         F, E1           1         0         F, E2           1         1         reserved |

| EXTSMI#(PX3_KRSMIREQ#)              | V20   | 0   | 0: Enable by KBD SMI or RTC wake                                                                                                                                         |

### Table 1-12GPIO Port Definition Map I

| GPIO/Signal              | Pin # | I/O | Description                                      |

|--------------------------|-------|-----|--------------------------------------------------|

| GPI1 (DK3_DOCKIRQ#)      | P19   | 0   | 0: Detect Docking IRQ                            |

| GPI2/REQA# (PX3_OEM0)    | M1    | 0   | OEM detection                                    |

| GPI3/REQB# (SM5_BAYSW)   | N2    | 0   | Detect FDD/CD bay 1: installed, 0: not installed |

| GPI4/REQC# (CF5_FDD/CD#) | P3    | 0   | Detect FDD or CD installed 1: FDD, 0: CD         |

| GPI5/APICREQ#            | K18   | 0   | NC                                               |

| GPI6/IRQ8# (RT3_IRQ8#)   | Y20   | 0   | 0: RTC wake                                      |

| GPI7/SERIRQ (PM3_IRQSER) | J19   | 0   | Serial IRQ                                       |

| GPI8/THRM# (SM5_OVTMP#)  | H19   | 0   | 0: Enable over temperature of CPU or system      |

| GPI9/BATLOW# (PX3_OEM1)  | U19   | Ι   | OEM detection                                    |

| GPI10/LID                | P16   | I   | NC                                               |

| GPI11/SMBALER#           | N17   | I   | NC                                               |

| GPI12/RI# (PX3_RI#)      | P18   | I   | 0: Enable by Ring indicator input                |

| GPI13 (PT3_MID0)         | L2    | I   | Detect MMO module revision                       |

| GPI14 (PT3_MID1)         | J3    | I   | Detect MMO module revision                       |

| GPI15 (PT3_MID2)         | L5    | I   | Detect MMO module revision                       |

| GPI16 (PT3_MID3)         | K3    | I   | Detect MMO module revision                       |

| GPI17 (SM5_FLOATREQ#)    | K4    | I   | Detect float request from SMC                    |

| GPI18 (PX3_FLASHRCY#)    | H1    | I   | 0: Enable flash BIOS recovery                    |

| GPI19 (PX3_VGACT)        | H4    | I   | 1: Detect VGA activity                           |

| GPI20 (PM3_A_ACT/PD#)    | H5    | I   | Detect PCMCIA socket A activity for OZ6832       |

| GPI21 (PM3_B_ACT)        | G3    | Ι   | Detect PCMCIA socket B activity                  |

Table 1-13GPIO Port Definition Map II

| GPIO                         | I/O | Description       |  |  |

|------------------------------|-----|-------------------|--|--|

| GPIO Pin Assignment: 80C51SL |     |                   |  |  |

| LED 0 (KB5_MIREQ#)           | 0   | ANI3 (KB5_PANID3) |  |  |

| LED 1 (KB5_NUMLED#)          | 0   | PAD LED control   |  |  |

| LED 2 (KB5_CAPLED#)          | 0   | CAP LED control   |  |  |

| LED 3 (KB5_KEYLICK)          | 0   | Keyclick output   |  |  |

| P1.0                         | 0   | NC                |  |  |

| P1.1                         | 0   | NC                |  |  |

| P1.2                         | 0   | NC                |  |  |

| P1.3                         | 0   | NC                |  |  |

| P1.4                         | 0   | NC                |  |  |

| P1.5                         | 0   | NC                |  |  |

| P1.6                         | 0   | NC                |  |  |

### Table 1-13 GPIO Port Definition Map II

| GPIO I/O                   |    | Description                                      |  |

|----------------------------|----|--------------------------------------------------|--|

| P1.7 (IS5_IRQ12)           | 0  | IRQ12                                            |  |

| P2.0 (KB5_MEMB0A0)         |    | Address 0 of memory bank 0                       |  |

| P2.1 (KB5_MEMB0A1)         |    | Address 1 of memory bank 0                       |  |

| P2.2 (KB5_MODE)            | I  | Detect KBD mode (1:US/EC 0:Japan)                |  |

| P2.3                       | I  | NC                                               |  |

| P2.4 (KB5_MEMB1A0)         | I  | Address 0 of memory bank 1                       |  |

| P2.5 (KB5_PSWD)            | I  | Enable Password                                  |  |

| P2.6 (KB5_MEMB1A1)         | I  | Address 1 of memory bank 1                       |  |

| P2.7 (PX3_OEM0)            | I  | Address 1 of memory bank 1                       |  |

| P3.0 (SM5_TXD)             | 1  | Receiving data from SMC to KBC                   |  |

| P3.1 (SM5_RXD)             | 0  | Transmitting data from KBC to SMC                |  |

| P3.2 (KB5_KBDCLK)          | 0  | External KB clock                                |  |

| P3.3 (KB5_PTRCLK)          | 0  | External PS/2 clock                              |  |

| P3.4 (KB5_KBDDAT)          | 0  | External KB data                                 |  |

| P3.5 (KB5_PTRDAT)          | 0  | External PS/2 data                               |  |

| P3.6 (KB5_TOUCHWR*)        | 0  | Write enable touch pad data                      |  |

| P3.7 (KB5_TOUCHRD*)        | 0  | Read enable touch pad data                       |  |

| ANI0 (KB5_PANID0)          | 1  | Panel ID                                         |  |

| ANI1 (KB5_PANID1)          | 1  | Panel ID                                         |  |

| ANI2 (KB5_PANID2)          | 1  | Panel ID                                         |  |

| ANI3 (KB5_PANID3)          | 1  | Panel ID: 3 2 1 0 0 0 0 0 12.1" TFT              |  |

| GPIO Pin Assignment: 83C55 | 2  |                                                  |  |

| P0.0(SM5_CHARGEON#)        | 0  | Charge control enable                            |  |

| P0.1                       | 0  | NC                                               |  |

| P0.2 (SM5_BMCPWREN#)       | 0  | BMC VCC power enable                             |  |

| P0.3 (SM5_P3/5VRON#)       | 0  | 3V and 5V power on                               |  |

| P0.4 (SM5_SUSPEND)         | 0  | Suspend control enable                           |  |

| P0.5 (SM5_PWRLED#)         | 0  | Power LED                                        |  |

| P0.5 (SM5_PWRLED#)         | 0  | Battery LED                                      |  |

| P0.7 (SM5_SMIREQ#)         | 0  | SMC SMI request                                  |  |

| P1.0 (SI5_PNF)             | 1  | Detect Printer or external FDD 0: FDD 1: Printer |  |

| P1.1 (SM5_1WIRE)           | 10 | Dallas protocol                                  |  |

| P1.2 (SM5_UNDOCK_REQ#) I   |    | Undocked request                                 |  |

| P1.3 (PX3_CPUSTP#) I       |    | Detect CPU clock stop                            |  |

| P1.4 (SM5_ATN#) IO         |    | I2C inturrupt                                    |  |

| P1.5 (SM5_RST#) IO         |    | I2C reset                                        |  |

| P1.6 (SM5_CLK#) IO         |    | I2C clock                                        |  |

| P1.7 (SM5_DAT#)            | 10 | I2C data                                         |  |

## Table 1-13GPIO Port Definition Map II

| GPIO                   | I/O | Description                                   |

|------------------------|-----|-----------------------------------------------|

| P2.0                   | I   | NC                                            |

| P2.1                   | 0   | NC                                            |

| P2.2 (SM5_BAYSW)       | I   | Detect FDD/CD bay installed or not            |

| P2.3                   | 0   | NC                                            |

| P2.4                   | 0   | NC                                            |

| P2.5                   | 0   | NC                                            |

| P2.6                   | 0   | NC                                            |

| P2.7                   | 0   | NC                                            |

| P3.0 (SM5_RXD)         | Ι   | Receiving data from KBC to SMC                |

| P3.1 (SM5_TXD)         | 0   | Transmitting data from SMC to KBC             |

| P3.2 (SM5_DOCKSW)      | Ι   | Dock switch sense                             |

| P3.3 (CF5_DOCKED)      | I   | Detect completely docked or not               |

| P3.4 (SM5_LIDSW)       | I   | Lid switch sense                              |

| P3.5 (SM5_OVTMP#)      | 0   | CPU or system over temperature                |

| P3.6                   | 0   | NC                                            |

| P3.7 (SM5_ON_RES_SW)   | 0   | ON/RESUME switch for Japan version            |

| P4.0 (SM5_FANON)       | 0   | Fan control                                   |

| P4.1                   |     | NC                                            |

| P4.2 (SM5_FLOATREQ#)   | 0   | Docking float request                         |

| P4.3 (SM5_UNDOCK_GNT#) | 0   | Undock grant                                  |

| P4.4 (SM5_ICONT)       | Ι   | Charge current control                        |

| P4.5 (SM5_FLAOTGNT#)   | I   | Docking float grant                           |

| P4.6 (SM5_PWRRDYB)     | 0   | Power ready, delay about 4ms after power good |

| P4.7 (SM5_SYSRDY)      | 0   | NC                                            |

| P5.0 (CHARGSP)         | Ι   | Charging set point                            |

| P5.1 (SM5_VBAT_MAIN)   | Ι   | Main battery detection                        |

| P5.2 (SM5_ACPWRGD)     | I   | AC source power good                          |

| P5.3 (SM5_NBPWRGD)     | Ι   | 3V, 5V, processor module power good           |

| P5.4 (SM5_ATFINT)      | Ι   | CPU thermal interrupt (panic)                 |

| P5.5 (SM5_THERM_SYS)   | I   | System thermal input (analog)                 |

| P5.6 (SM5_ACIN_AUX)    | I   | Aux AC adapter in                             |

| P5.7 (SM5_ACIN_MAIN)   | I   | Main AC adapter in                            |

| PWM1# (SM5_CONT)       | 0   | LCD contrast                                  |

| PWM0# (SM5_BRIT)       | 0   | LCD brightness                                |

## 1.6.6 PCI Devices Assignment

| Device                                      | Device ID | Assignment        |

|---------------------------------------------|-----------|-------------------|

| MTXC North Bridge                           | 0         | AD11              |

| PIIX4 ISA Bridge                            | 1         | AD18 (Function 0) |

| PIIX4 IDE controller                        | 1         | AD18 (Function 1) |

| PIIX4 USB controller                        | 1         | AD18 (Function 2) |

| PIIX4 PM/SMBUS controller                   | 1         | AD18 (Function 3) |

| PCI VGA(NM2160)                             | 2         | AD13              |

| PCI Cardbus controller                      | A         | AD21              |

| PCI Ethernet (Am79C970A) (ACER Dock<br>III) | С         | AD23              |

| PCI CardBus (TI 1131) (ACER Dock V)         | С         | AD23              |

## 1.6.7 Power Management

Power Management in this design is aimed toward the conservation of power on the device and system level when the devices or system is not in use. This implies that if any device is detected as not active for a sustained period of time, the device will be brought to some lower power state as soon as practicable.

With the exception of thermal management, if a device has a demand upon it, full performance and bandwidth will be given to that device for as long as the user demands it. Power management should not cause the user to sacrifice performance or functionality in order to get longer battery life. The longer battery life should be obtained through managing resources not in use.

Pathological cases of measuring CPU speed or trying to periodically check for reaction time of specific peripherals can detect the presence of power management. However, in general, since the device I/O is trapped and the device managed in SMI, the power management of devices should be invisible to the user and the application.

Thermal management is the only overriding concern to the power management architecture. By definition, thermal management only comes into play when the resources of the computer are used in such a way as to accumulate heat and operate many devices at maximum bandwidth to create a thermal problem inside the unit. This thermal problem indicates a danger of damaging components due to excessively high operating temperatures. Hence, in order to maintain a safe operating environment, there may be occasions where we have to sacrifice performance in order to achieve operational safety.

Heuristic power management is designed to operate and adapt to the user while the user is using it. It is the plug and play equivalent for power management. There are no entries in BIOS Setup which are required to be set by the user in order to optimize the computers battery life or operation. The only BIOS Setup entries are for condition information for suspend/resume operations. Normal operations and power management are done automatically. (see chapter 3 for details).

Since the power management is implemented by linking with APM interface closely, the APM function in Win95 or Win3.1 must be enabled and set to advanced level for optimum power management and the driver that installed in system must be Acer authorized and approved.

#### 1.6.7.1 PMU Timers

There are several devices related timers available on the V1-LS chip. Each timer may have zero or more devices assigned to the timer for the purpose of retriggering the timer.

| Item                         | Descriptions                                                                                                                                                                                                                                                |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Video timer                  |                                                                                                                                                                                                                                                             |

| Timer value                  | 30sec, 1min, 1.5min, 2min, 2.5min, 3min, 3.5min, 4min, 4.5min, 5min, 6min, 7min, 8min, 9min, 10min, 15min, 20min, 30min(if AC plugged-in)                                                                                                                   |

| System activities            | System activities                                                                                                                                                                                                                                           |

| and timer<br>retriggers      | <ul> <li>The video display (CRT and LCD) is in power saving mode.</li> </ul>                                                                                                                                                                                |

| louiggolo                    | Timer retriggers                                                                                                                                                                                                                                            |